在always块中,使用阻塞赋值(=)和非阻塞赋值(<=)的数据改变时期不同,

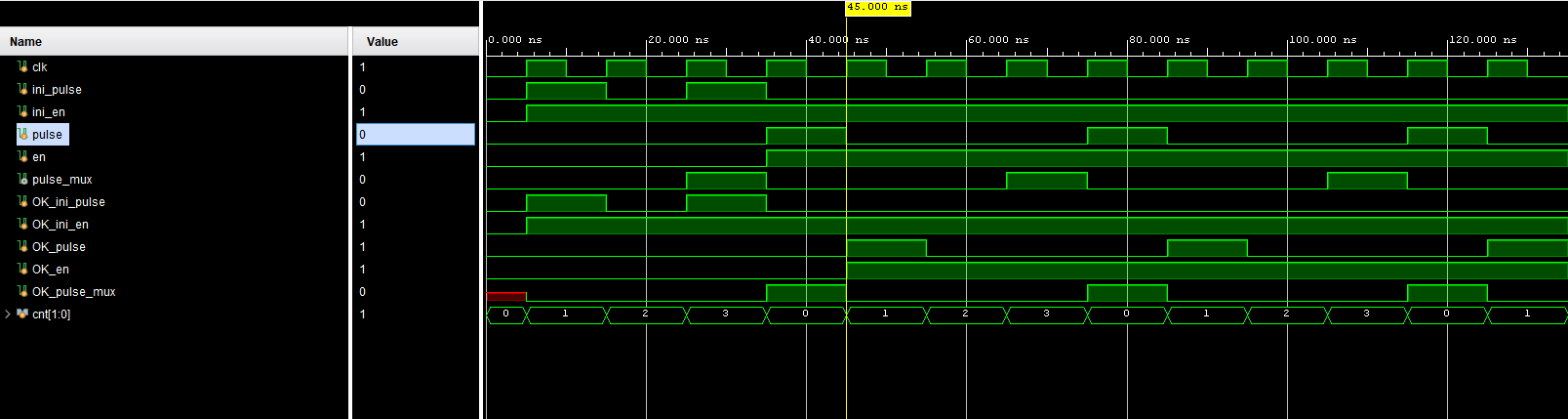

使用阻塞赋值,数据在时钟上升沿将马上改变,非阻塞赋值,数据在时钟周期结束后才改变,具体仿真如下

针对ini_pulse、ini_en、pulse、en这四个信号生成四个OK响应信号,ini_pulse、ini_en经过阻塞赋值其响应信号马上就发生了改变,pulse、en为非阻塞赋值,在一个周期后响应信号才发生改变

`timescale 1ns / 1ps

module test_tb();

reg clk;

reg ini_pulse=0;

reg ini_en=0;

reg pulse=0;

reg en=0;

wire pulse_mux;

reg OK_ini_pulse=0;

reg OK_ini_en=0;

reg OK_pulse=0;

reg OK_en=0;

reg OK_pulse_mux;

always begin

#5 clk = ~clk; // 写时钟周期为 10ns

end

initial begin

clk=0;

@(posedge clk)

ini_en=1; //拉高使能

ini_pulse=1;//生成脉冲

@(posedge clk)

ini_pulse=0;

#10

ini_pulse=1;

#10

ini_pulse=0;

#100;

$stop;

end

reg[1:0]cnt=0;

assign pulse_mux = (cnt==3) ? 1:0;//pulse_mux和pulse信号相比早一个周期,但是其响应信号还是会晚一个周期

always @(posedge clk )

begin

if(cnt==3)begin

pulse<=1;//把“<=”改成“=”你会发现响应信号会马上响应

en<=1;

cnt<=0;

end

else begin

cnt<=cnt+1;

pulse<=0;

end

end

always @(posedge clk )

begin

if(ini_pulse) OK_ini_pulse<=1;

else OK_ini_pulse<=0;

if(ini_en) OK_ini_en<=1;

else OK_ini_en<=0;

if(pulse) OK_pulse<=1;

else OK_pulse<=0;

if(en) OK_en<=1;

else OK_en<=0;

if(pulse_mux) OK_pulse_mux<=1;

else OK_pulse_mux<=0;

end

endmodule

Comments NOTHING