无符号数与有符号数相乘

只需要高位补0的同时用signed函数即可,位宽也是正常加,已经仿真验证过

如果不这样做,会自动把s_a也转化成无符号数

reg signed[7:0]s_a=-128;

reg [7:0]u_a=255;

wire signed[15:0]s_b=s_a*$signed({1'b0,u_a});有符号数取反

有些情况数值不会达到最小值,可以直接取反,不用做判定

//有符号数取反

//如果直接取反,当被取数为最小值-128,得到的结果还是-128,因为溢出了,除非阔一位才能得到+128

wire signed[7:0]s_c=-s_a;

wire signed[7:0]s_d;

assign s_d=(s_a==-(2**7)) ? (2**7-1):-s_a;整流

整流后的数据位宽可以小一位

wire [6:0]u_e;

assign u_e=(s_a>0) ? s_a : (s_a==-(2**7)) ? (2**7-1):-s_a;无符号数与有符号数加减

同样,无符号数需要signed并高位补零,如果不signed结果也会错误

//有符号数与无符号数加减

wire signed [8:0]s_g=s_a-$signed({1'b0,s_e});无符号数与无符号数加减

可以直接转化为有符号数

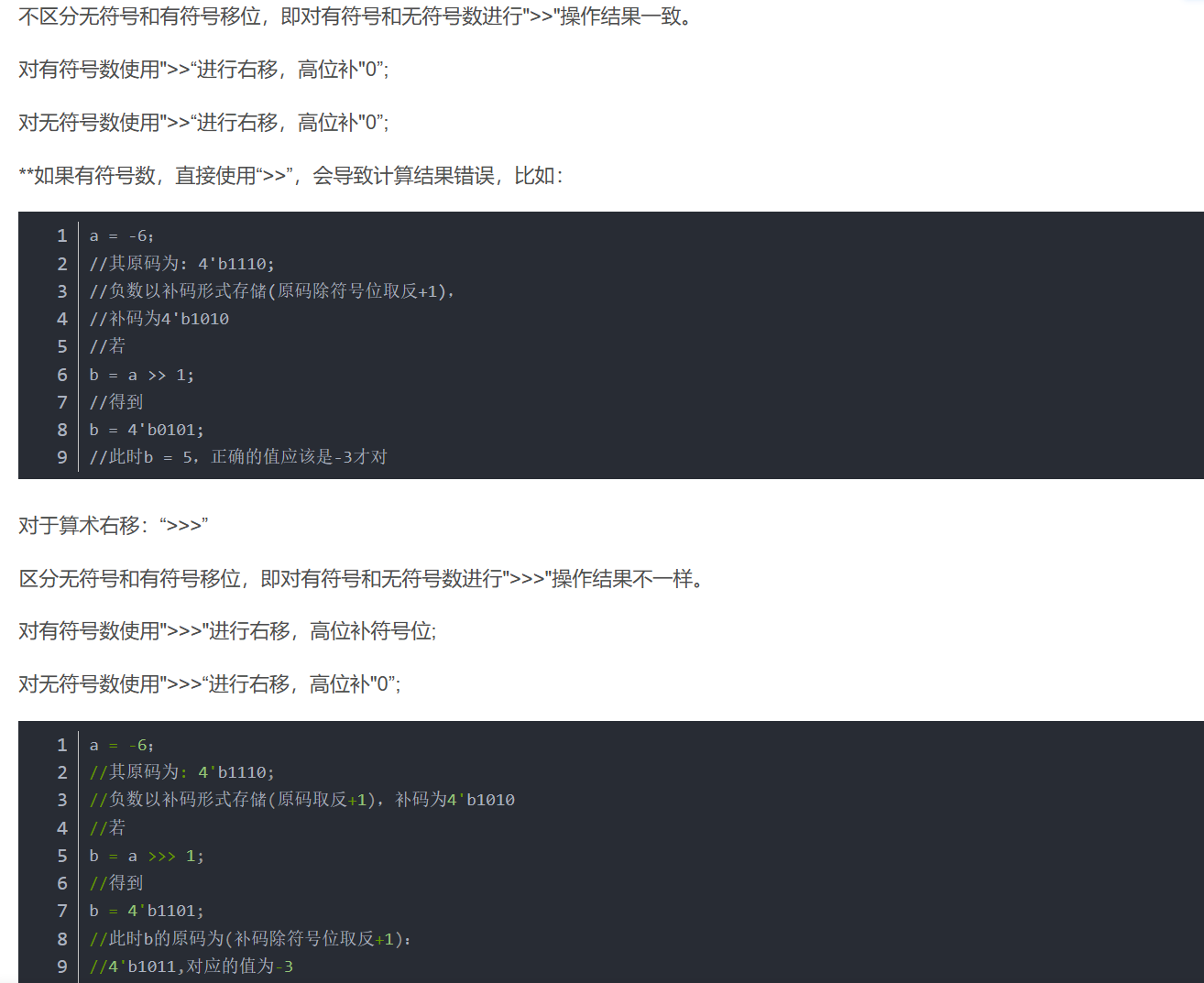

wire signed [8:0]s_f=u_e-u_a;无符号数与有符号数移位

注意:“>>>”移位符号也需要声明有符号数,不然也只会逻辑右移

Comments NOTHING