STM32fc8t6单片机最小系统板设计

软件:立创EDA专业版

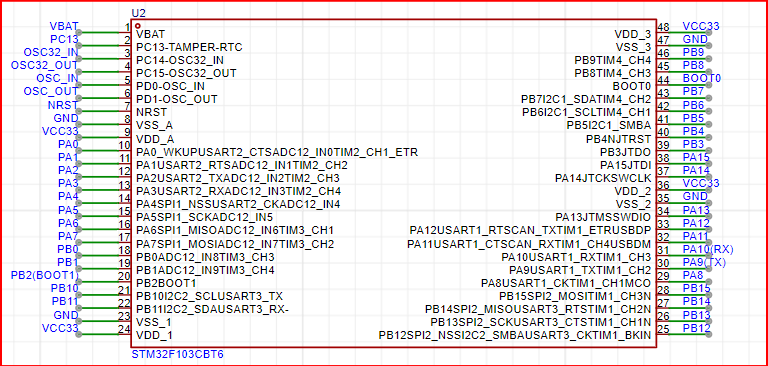

第一章:主控芯片

- 选择芯片STM32fc8t6

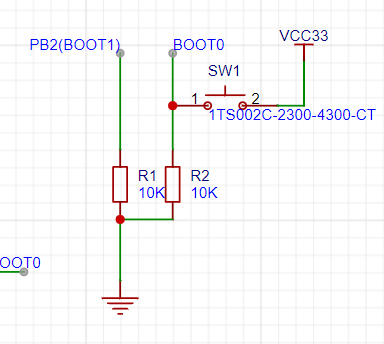

- 单片机启动原理(BOOT):分为三种启动模式,主要选择以主闪存存储器为启动区域,BOOT0引脚置1,BOOT1引脚接地,在实际设计时,两个引脚均需串一个电阻接地。

- 选择开关:元件搜索按键,分类选择轻触开关,分装为SMD,6,3.5,4.3mm

- 连接效果如下

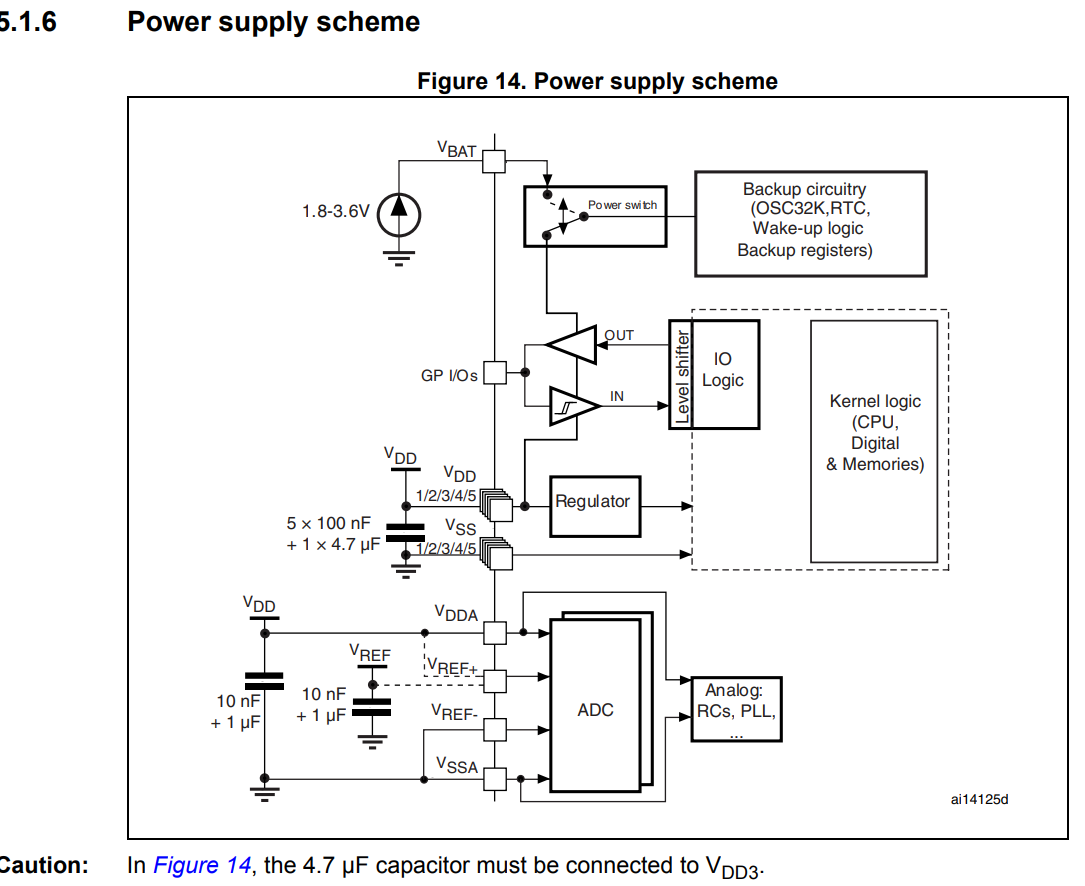

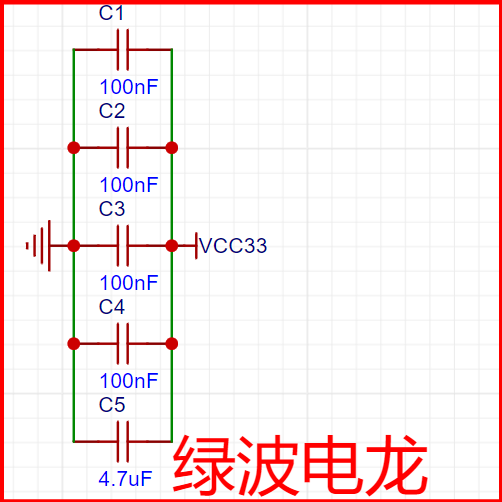

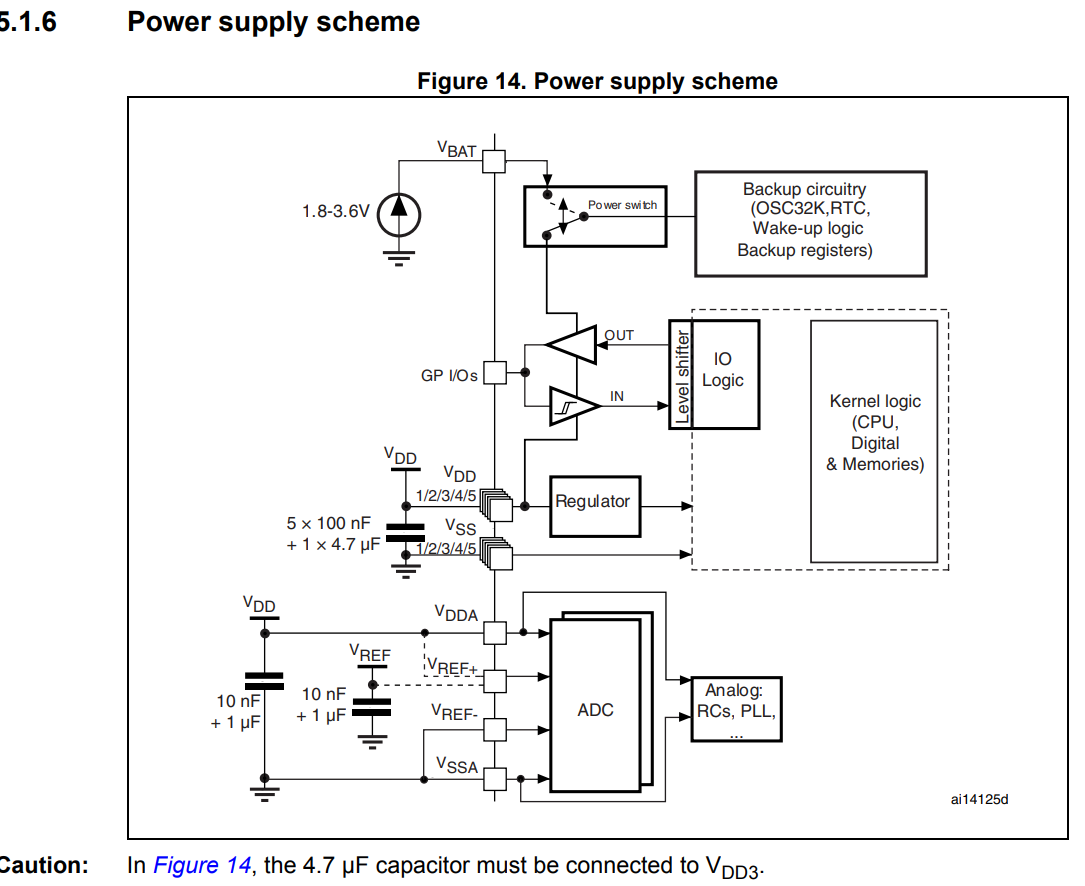

- 查看芯片手册:查看供电方案,在目录找,在第五章有一个Power supply scheme,点击进入,得到如下示意图

如上图,VDD需要接5个100nF和一个4.7uF的绿波电龙,连接电路如下图

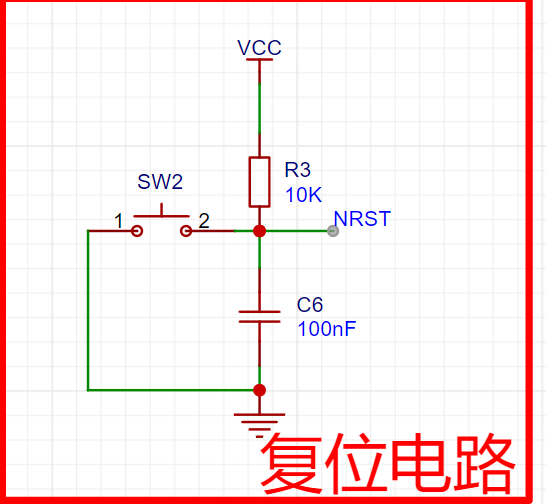

第二章:复位电路

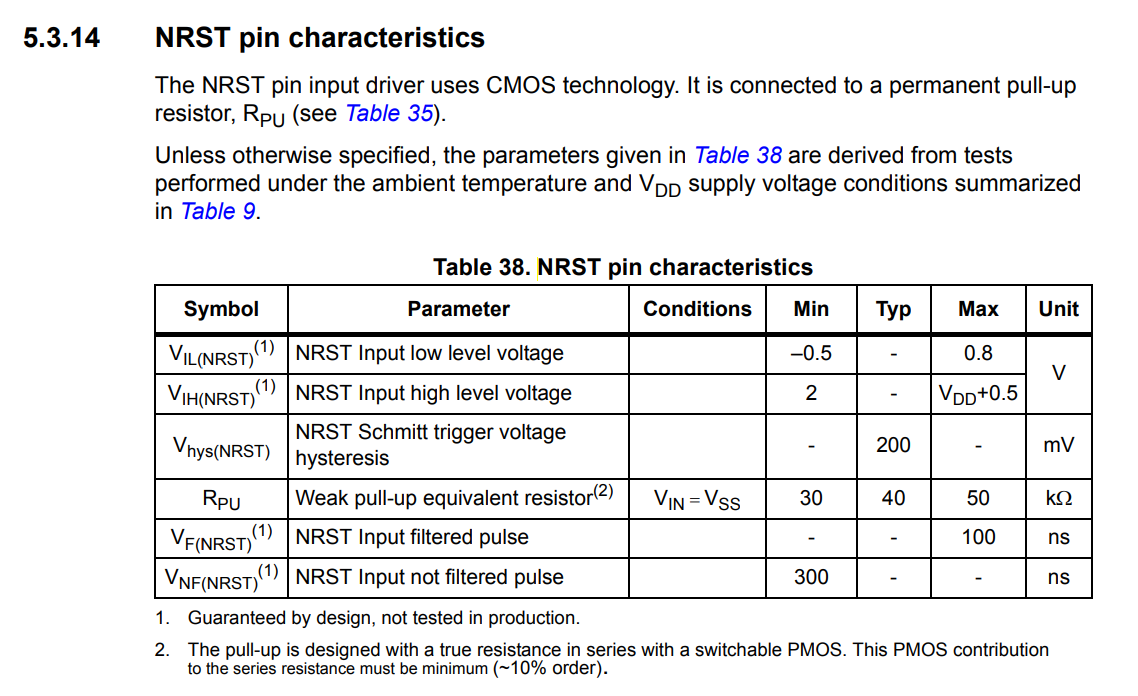

- 网络标签连接引脚NRST

- 打开数据手册,按下ctrl+F键使用搜索功能,搜NRST,在目录中找到并点开

翻译得到NRST引脚连接到永久上拉电阻器,可以给低电平使其复位

- 设计如下复位电路

当开关按下时,NRST脚接低电平,系统复位,电容C6的作用为:进行按键消抖,必须得低电平一段时间才能复位

第三章:时钟电路

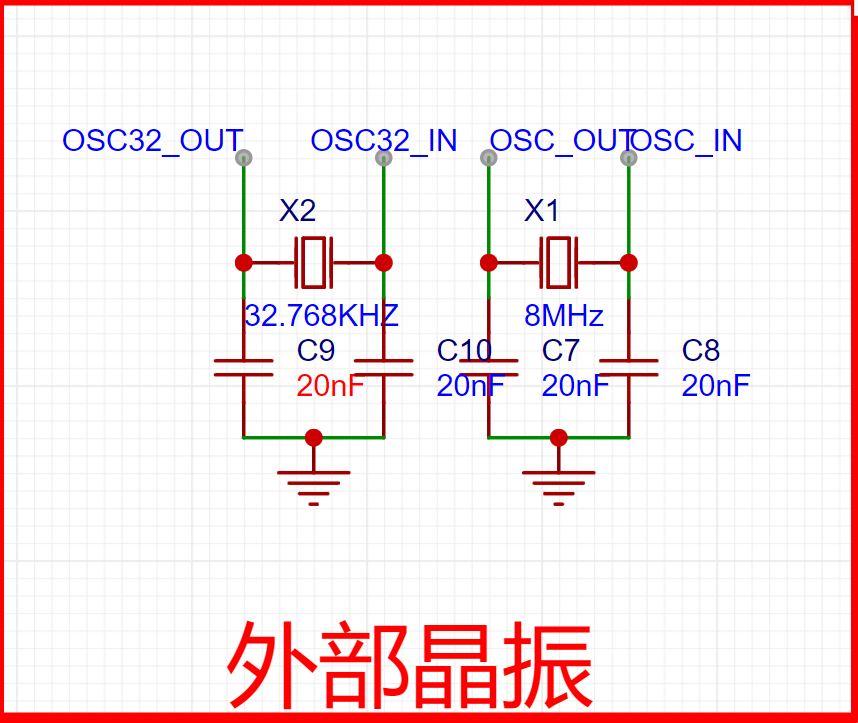

32单片机内部一般会有高速时钟和低速时钟,但是不够精准,需要外接一个晶振,外接的高速晶振一般为8MHz,通过倍频器可以达到72MHz,低速晶振为32.768KHz

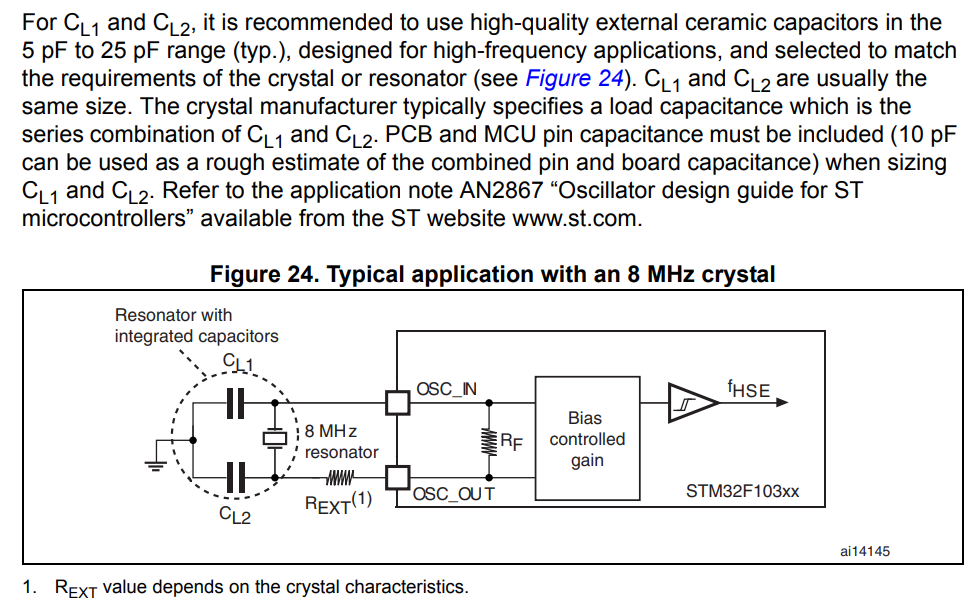

- 打开手册,在目录里找到外部晶振特点(External clock source characteristics),打开下滑,发现手册推荐的外部晶振和内部晶振分别为8MHz和32.768KHz,再往下滑,发现高速晶振的应用原理图

翻译上述文字:得知对于CL1和CL2,建议在5pF至25pF范围,还必须考虑PCB和MCU的引脚电容(==高速晶振10pF可以作为引脚和板电容的粗略估计,低速晶振为2PF到7PF之间==)

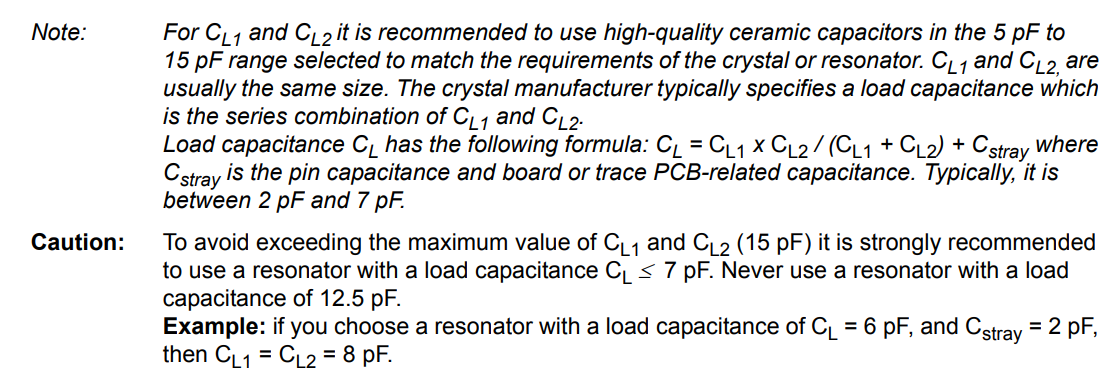

为了严谨,下图为==电容的计算公式==

翻译:

:对于CL1和CL2,建议使用5pf到的高质量陶瓷电容器15pf范围的选择,以配合要求的晶体或谐振器。CL1和CL2是==通常大小相同==。晶体制造商通常指定负载电容为CL1与CL2的级数组合。

负载电容CL有如下公式:CL = CL1 × CL2 / (CL1 + CL2) + Cstray,其中

Cstray是指引脚电容与电路板或走线pcb相关的电容。

注意:为避免超过CL1和CL2的最大值(15pf),强烈建议使用

使用带负载电容CL7 pF的谐振器。不要使用带负载的谐振器

电容为12.5 pF。

例如:==如果选择一个负载电容CL = 6pf, Cstray = 2pf的谐振器,==

==则CL1 = CL2 = 8pf==

- 搜索晶振:在器件菜单搜索8M晶振,搜编号C93660,低速晶振搜编号C93229,发现高速晶振参数为20pF,即CL=20pf,带入公式计算,令引脚电容为10pF,得CL1=CL2=20pF,低速晶振参数为CL=12.5PF,令引脚电容为2.5pF,得CL1=CL2=20PF。

- 引脚:外部高速晶振接OSC_IN和OSC_OUT两个端口,外部低速晶振接OSC32_IN和OSC32_OUT两个引脚,电路连接如图

第四章:电源

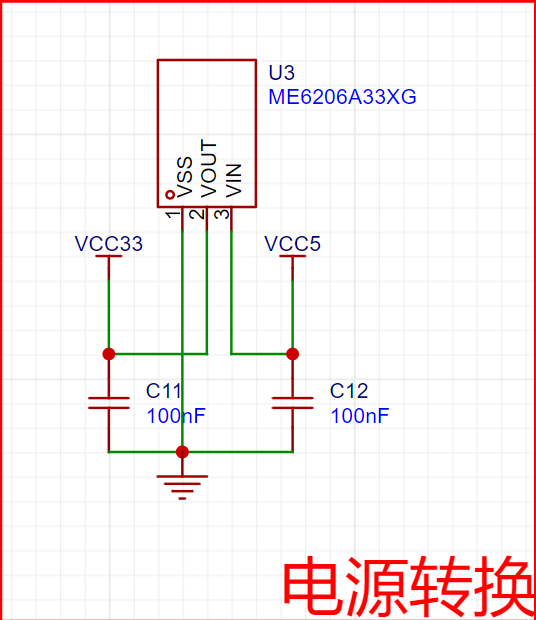

- 搜索LDO(线性稳压器),选择3.3V稳压器,搜编号C161345,芯片原理图如图所示

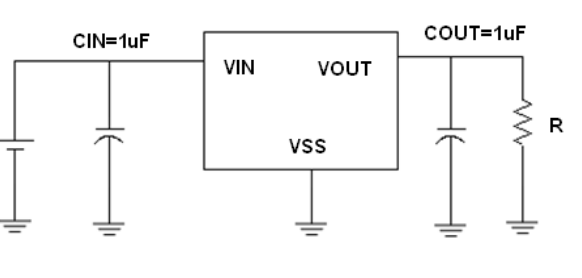

VIN为输入的引脚,VOUT为输出引脚,VSS一般接地,查看芯片手册,其电路连接如图

输入端和输出端均接1uF的绿波电龙。接线如下图

- 查看单片机电源供电电路原理图和说明

其中VSSA,VDDA=2.0至3.6V:用于ADC等模块,==VDDA和VSSA必须连接到VDD和VSS==

- 给单片机供电,VDD接正点,VSS接负电,给VDD引脚全部接上VCC33网络标签,VSS引脚全部接上GND

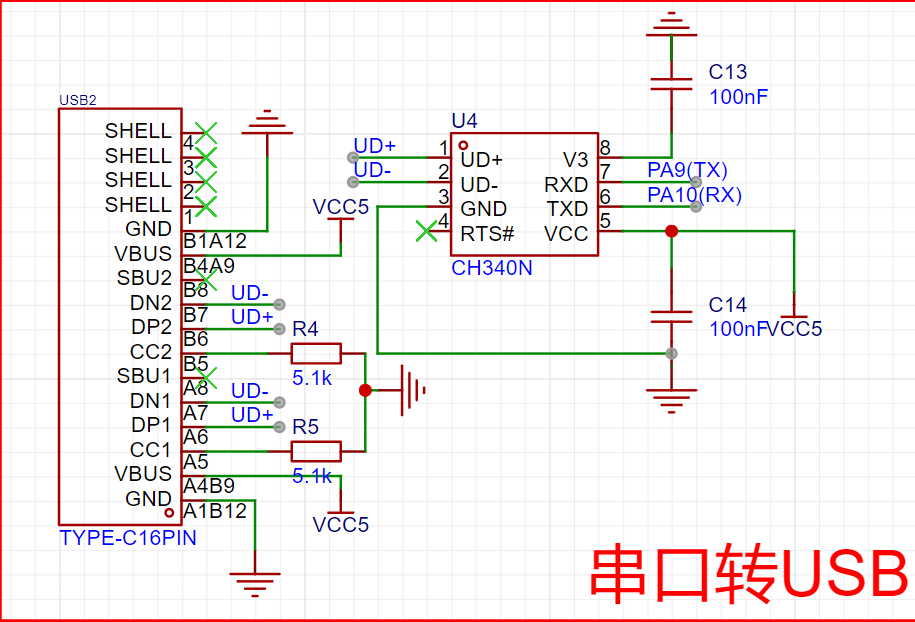

第五章:串口转USB

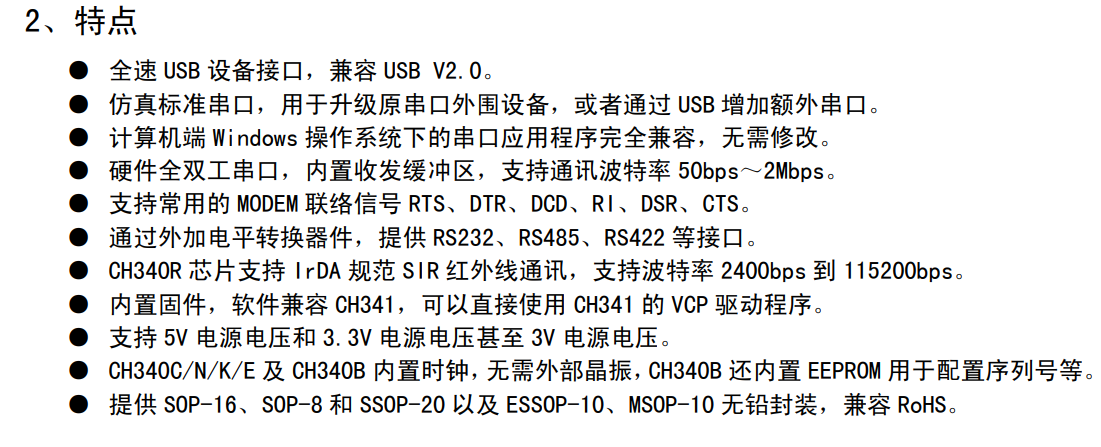

对于串口转USB模块,我们一般会选用CH340芯片

- 搜索CH340,随便找一个打开数据手册,找到特点和分装

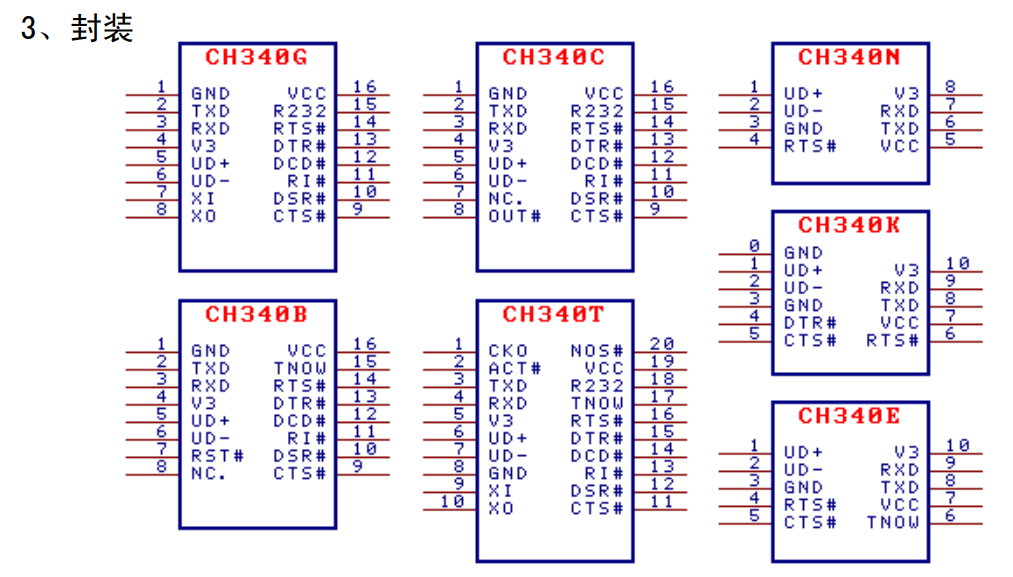

发现CH340B/C/N/K/E均内置时钟,由于是最小系统板,我们可以选择小分装CH340N。

-

下滑,在引脚界面找到各个引脚的用法

- VCC:正电源输入端,需要外接 0.1uF 电源退耦电容

- V3:在 3.3V 电源电压时连接 VCC 输入外部电源, 在 5V 电源电压时外接容量为 0.1uF 退耦电容

- UD+:直接连到 USB 总线的 D+数据线

- UD-:直接连到 USB 总线的 D-数据线

- RTS#:MODEM 联络输出信号,请求发送,低(高)有效,不接

- TXD:串行数据输出(CH340R 型号为反相输出)

- RXD:串行数据输入,内置可控的上拉和下拉电阻

-

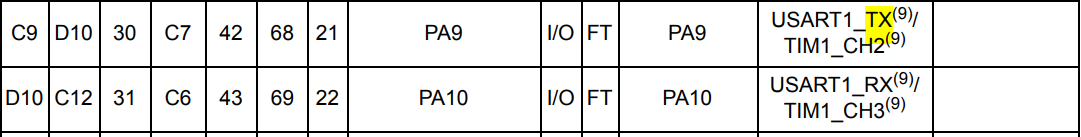

查芯片手册,ctrl+F搜索TX,如下图

==发现PA9是TX输出端,PA10是RX输入端,故PA9接RXD,PA10接TXD==

-

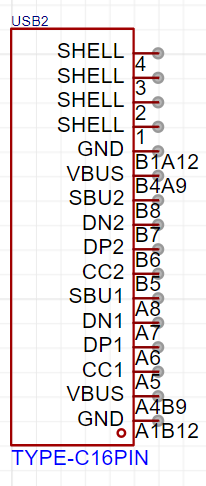

选择Type-c的USB,一定要选择16脚的,6脚的只能充电,16脚可以进行数据传输,以编号C393939的Type-C母座为例

以下为具体引脚的功能描述

其中较为重要的引脚有Dp和Dn,分别连接正负差分信号,上面的四个SHELL引脚均无用,SBU1和SBU2也用不到,VBUS接电源,为避免引脚冲突,CC1和CC2需要接5.1K的下拉电阻。

- 最终电路图如下:

第六章:PCB生产、测试

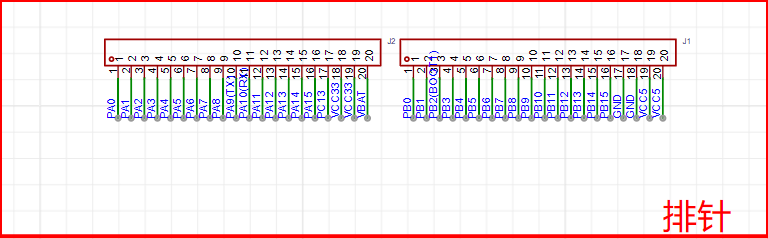

- 将芯片引脚全部引出,搜索1*20p的排针,一般间距为2.54mm,选好排针后,一一对应加上网络标号,如下

芯片引脚如下

-

PCB布线,点击右上角更新转换原理图

元器件摆放原则:

- 外部晶振靠近芯片,外部晶振的电容靠近外部晶振

- 滤波电容靠近芯片

- 其他元器件可以随便摆

Comments NOTHING