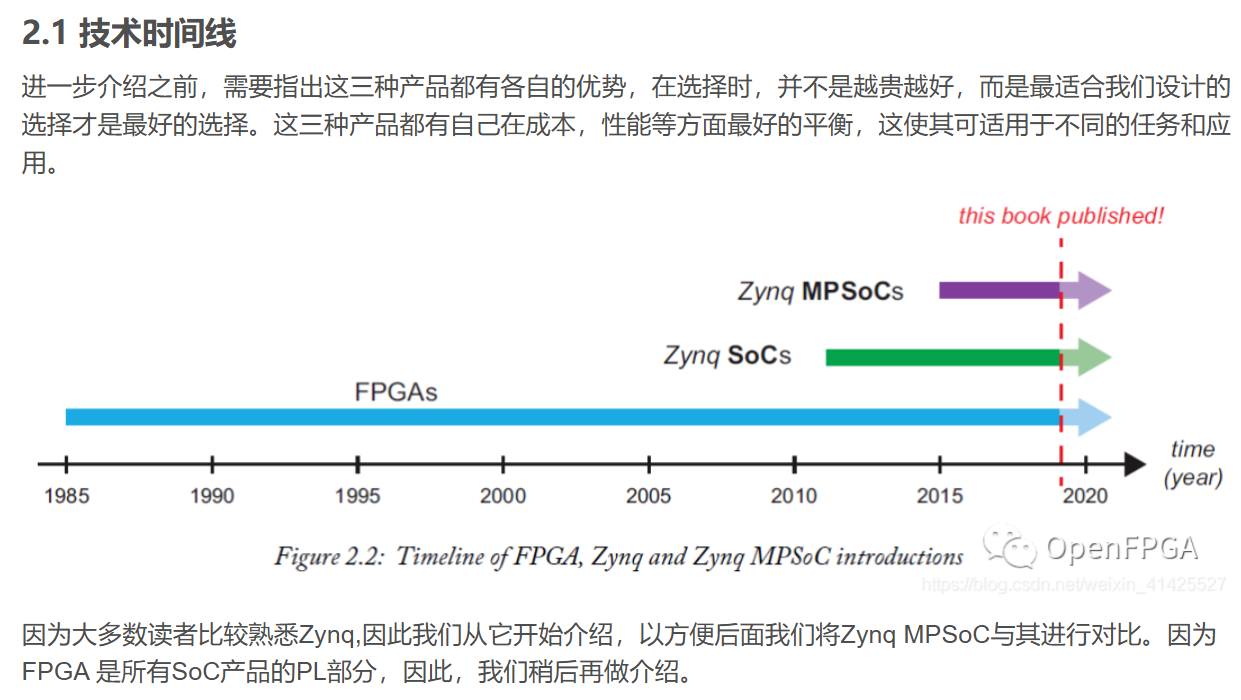

出现时间

zynq架构特征

Zynq-7000 SoC是Xilinx发布的第一款SoC器件。集成了基于FPGA的PL部分和基于Arm的PS部分。这里只对其做简单介绍。更详细介绍可参考[The Zynq Book](http://www.zynqbook.com/)该书已出中文版。

2.2.1 Zynq架构特征

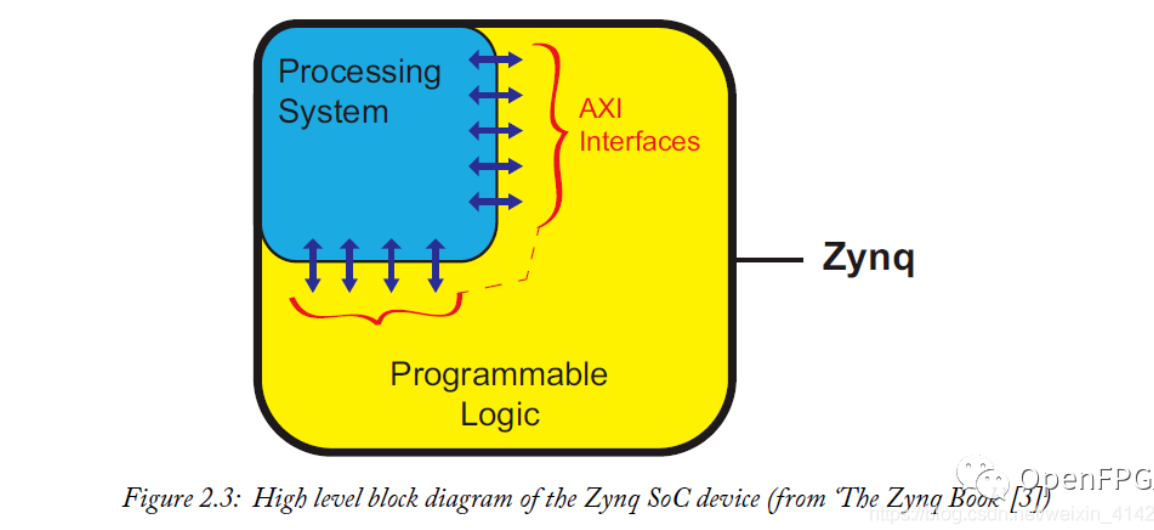

从高层次的角度去看,Zynq架构包含PS和PL两部分以及之间的互连线。如图2.3所示。互联遵循AXI标准,AXI标准是Arm开发的片上通信技术标准。

将PS和PL集成到一起一方面能够为运行嵌入式系统中的基于软件的部分提供专用的优化的资源(我的理解是适合运行于处理器的部分),另一方面能够发挥FPGA的优势(尤其时其并行性和可配置能力)。AXI接口来连接这两个不放呢,AXI是专为SoC应用优化的一个接口标准。

图2.3中并不是按尺寸比例画的,对于不同的Zynq器件,他们有相同的PS架构,但是PL部分的尺寸不同。而对于Zynq和Zynq MPSoC,其PS和PL部分都是不同的。

Zynq PS部分

如图2.3的蓝色部分,是一个应用级的处理器以及相关元件。如下所示:

应用处理单元Application Processor Unit (APU) -这部分包括一个双核 Arm Cortex-A9处理器,以及256KB的片上缓存。

互连线和存储接口 -用来进行PL和PS通信以及与各自的片外存储单元通信

I/O外设 -一系列集成的外设接口,包括一些常用的标准例如 USB,UART,SPI,I2C等

Zynq的PS部分包含两个处理核,这使得设计人员可以在两个核上运行相同操作系统,或者每个核运行一个不同的操作系统。后面我们会对比Zynq核Zynq MPSoC的PS架构,并说明新器件增加的一些功能,实际上,Zynq MPSoC具有6个处理核。

最近(应该是2019年),一个轻量级的Zynq版本,Zynq-7000S发布,该版本PS只包含一个Cortex-A9的处理器。

Zynq PL部分

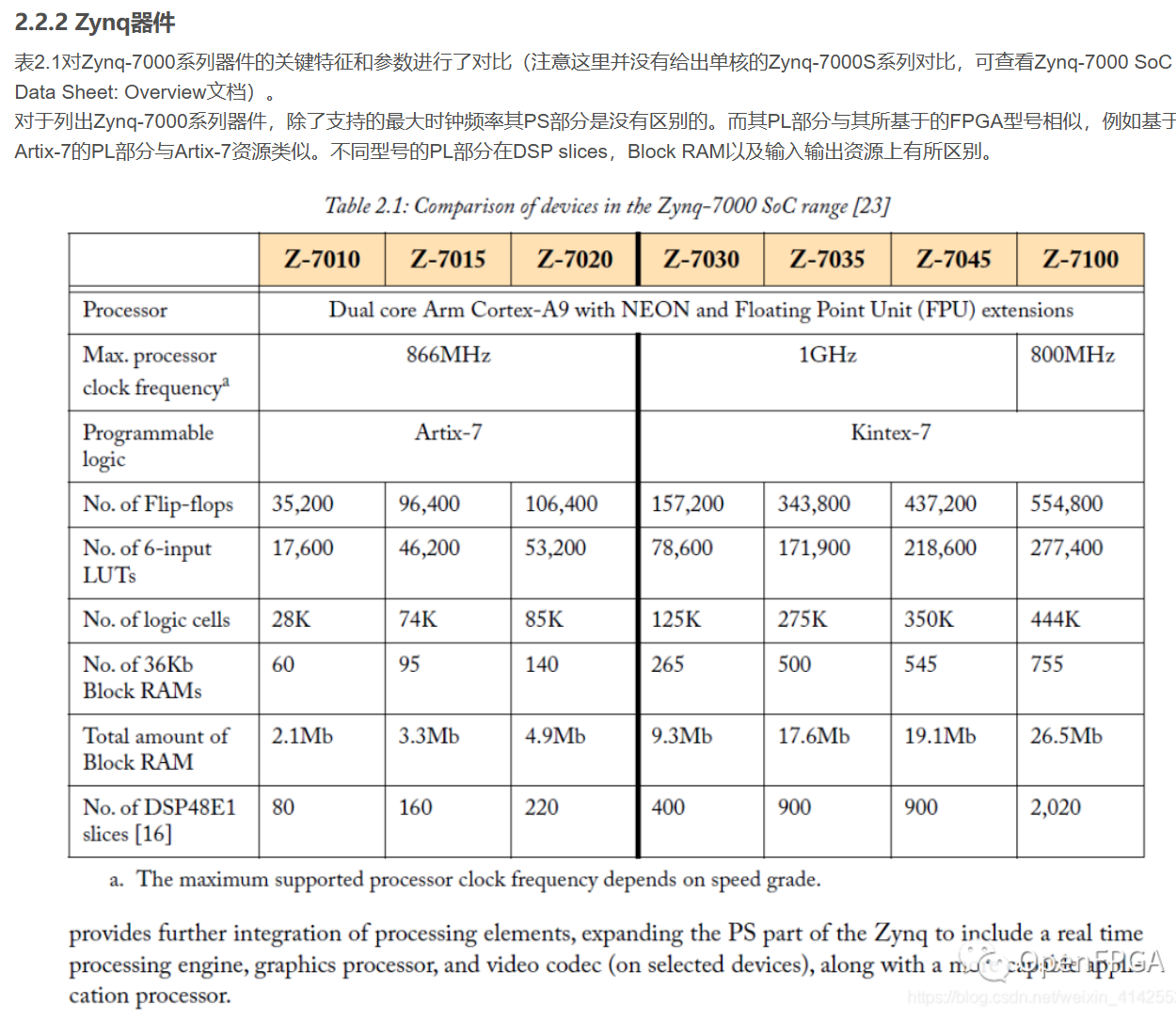

Zynq的PL部分是基于Xilinx的FPGA器件的,其PL部分所对应的器件性能决定PL性能,包括Xilinx的Artix-7,Kintex-7以及Virtex-7系列器件。像这些FPGA一样,其PL部分包含DSP48x slices(高速计算资源),Block RAMs,高速收发器件,以及集成的通信模块。以及通用逻辑。2.4.3节对现代FPGA的这些模块进行进一步介绍。

Zynq PS与PL部分接口

Zynq的PL和PS部分有9个接口,包括4个“通用目的接口”,四个“高性能”接口,以及1个用来PS中APU和PL通信的“加速一致性”接口。

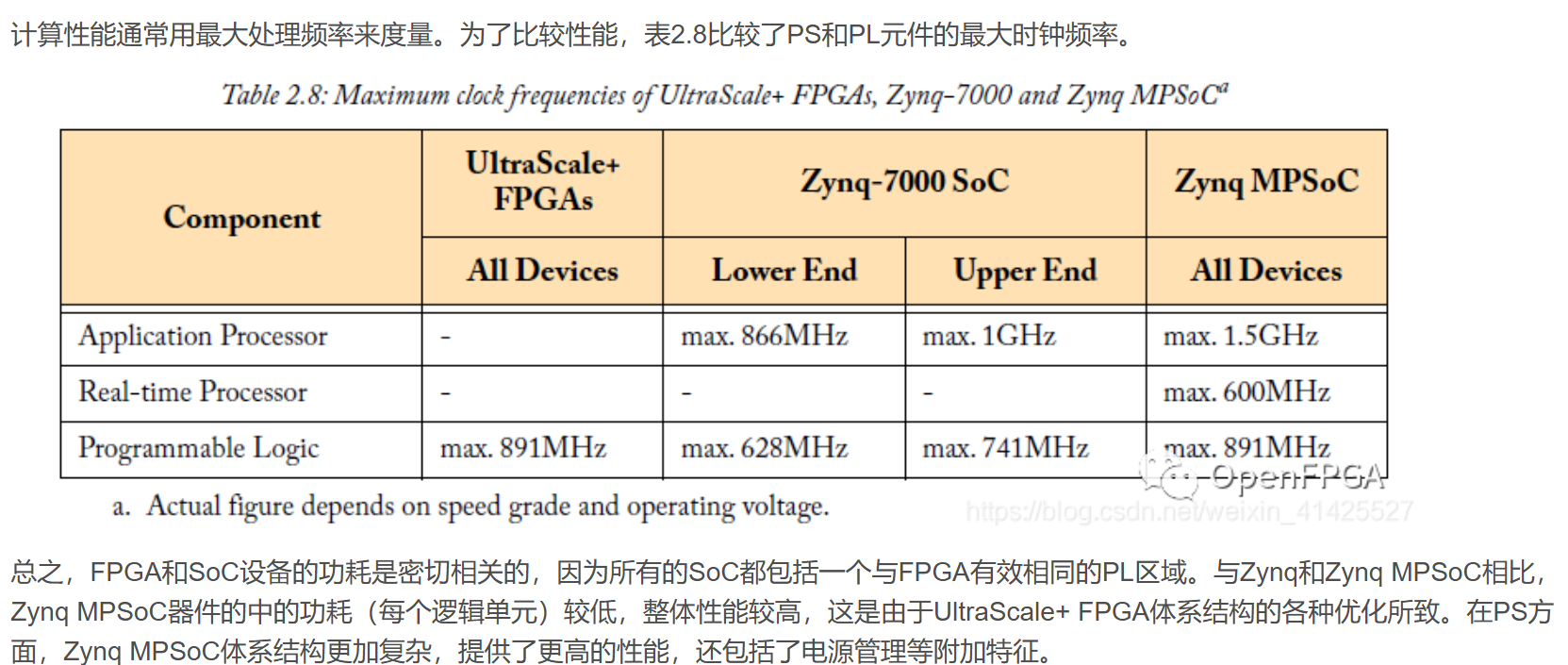

Comments NOTHING