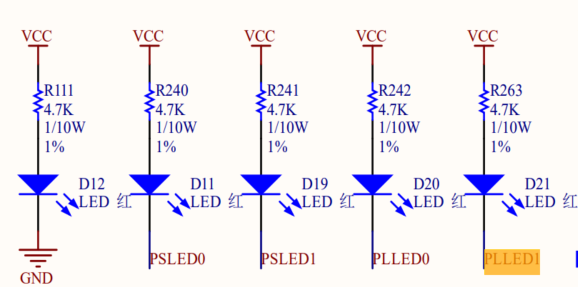

用户LED

PL电平1.8V。

| PLLED0 | K14 |

|---|---|

| PLLED1 | K10 |

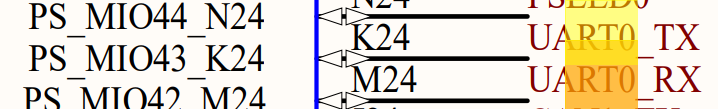

| PSLED0 | N24 |

| PSLED1 | P24 |

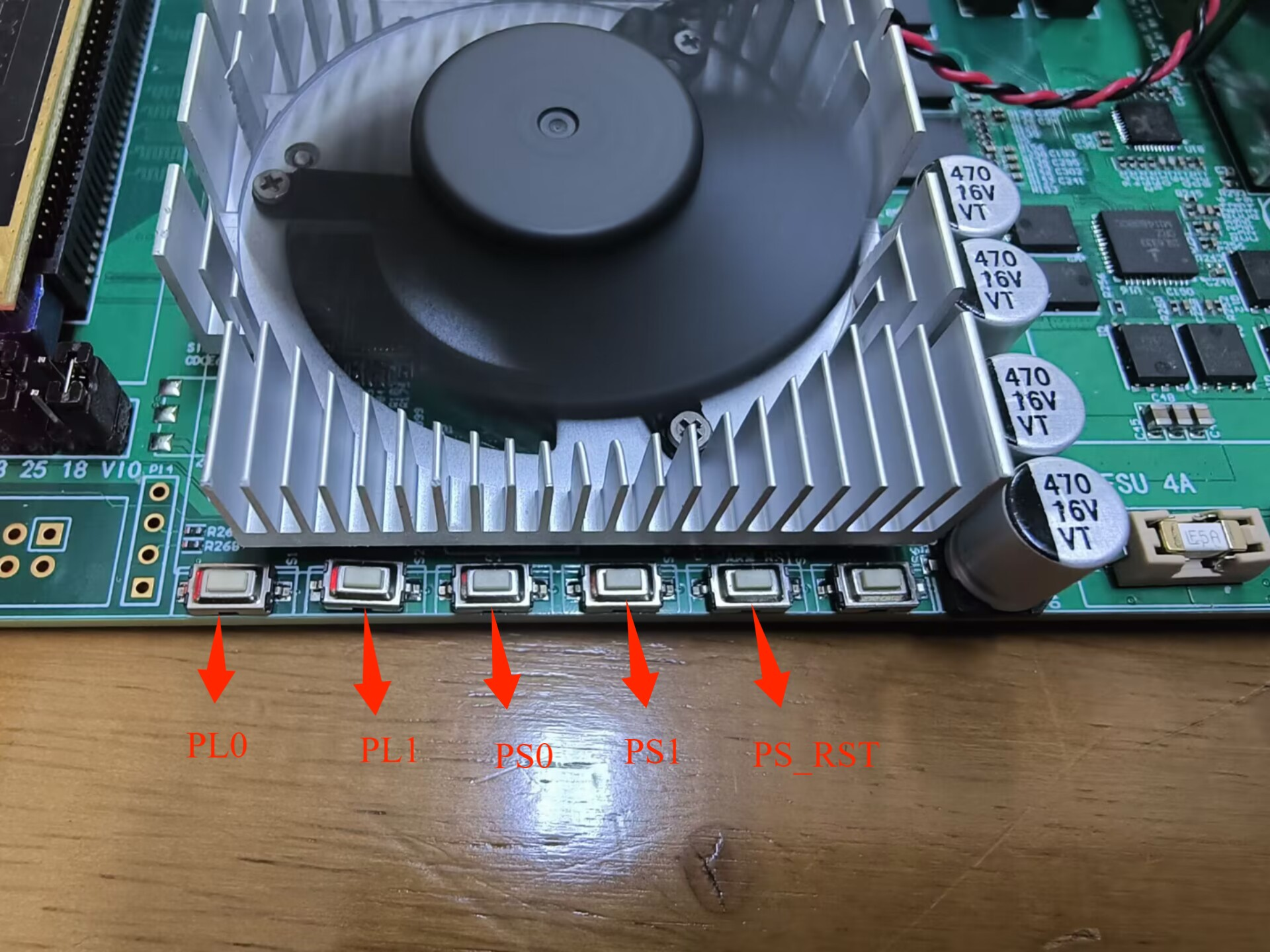

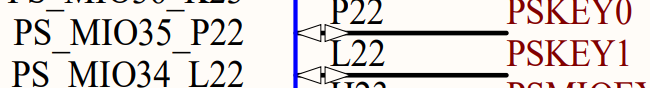

用户按键

PL电平1.8V

PS复位按键

下面这个按键目前不知道是干嘛用的

| PLKEY0 | V9 |

|---|---|

| PLKEY1 | W10 |

| PSKEY0 | MIO35 |

| PSKEY1 | MIO34 |

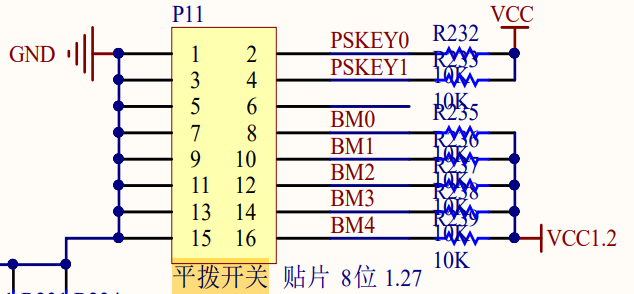

用户拨码开关

上面两个拨码接通会使PS端的按键失效

| BM0 | AE3 |

|---|---|

| BM1 | AJ5 |

| BM2 | AJ6 |

| BM3 | AJ4 |

| BM4 | AH4 |

PS端TTL转usb串口

40P排针

排针布局兼容黑金,17对差分线

NODENAME HDIO_CLK_P , U1 F12

NODENAME HDIO_CLK_N , U1 F11

NODENAME HDIO_15_P , U1 G15

NODENAME HDIO_15_N , U1 G14

NODENAME HDIO_14_P , U1 H16

NODENAME HDIO_14_N , U1 G16

NODENAME HDIO_13_P , U1 J14

NODENAME HDIO_13_N , U1 H14

NODENAME HDIO_12_P , U1 J16

NODENAME HDIO_12_N , U1 J15

NODENAME HDIO_11_P , U1 AE15

NODENAME HDIO_11_N , U1 AE14

NODENAME HDIO_10_P , U1 AF15

NODENAME HDIO_10_N , U1 AG15

NODENAME HDIO_09_P , U1 AE13

NODENAME HDIO_09_N , U1 AF13

NODENAME HDIO_08_P , U1 AG14

NODENAME HDIO_08_N , U1 AG13

NODENAME HDIO_07_P , U1 AH14

NODENAME HDIO_07_N , U1 AH13

NODENAME HDIO_06_P , U1 AJ15

NODENAME HDIO_06_N , U1 AJ14

NODENAME HDIO_05_P , U1 AK13

NODENAME HDIO_05_N , U1 AL12

NODENAME HDIO_04_P , U1 AK15

NODENAME HDIO_04_N , U1 AK14

NODENAME HDIO_03_P , U1 AL13

NODENAME HDIO_03_N , U1 AM13

NODENAME HDIO_02_P , U1 AM14

NODENAME HDIO_02_N , U1 AN13

NODENAME HDIO_01_P , U1 AN12

NODENAME HDIO_01_N , U1 AP12

NODENAME HDIO_00_P , U1 AN14

NODENAME HDIO_00_N , U1 AP14PS端两个用户MIO引出

时钟电路

SI5338时钟电路

SI5338通过I2C协议来驱动

一路有源晶振,给FPGA和SI5338提供时钟,一路25M无源晶振给SI5338单独提供时钟,也可以通过FPGA内部输出时钟来给SI5338

SI5338引出了PCIE时钟、两对PS差分时钟,以及一对PL端用户差分时钟

SI5338已经配置好默认输出200M差分到pl端

| PLCLK_P | AF7 | SI_SCL | H10 |

|---|---|---|---|

| PLCLK_N | AE7 | SI_SDA | J10 |

| FPGA_CLK_50M | AF6 | ||

| FPGA_GEN_CLK | J11 |

注意:PLCLK_P实际接入的是芯片的SYSCLK_200_N,PLCLK_N实际接入的是芯片的SYSCLK_200_P(反着来的,vivado对应的输入P信号就是AE7)

50M有源晶振没有焊接

外部差分时钟输入(改SMA接口)

| USER_CLK_P | T8 |

|---|---|

| USER_CLK_N | R8 |

PS端时钟

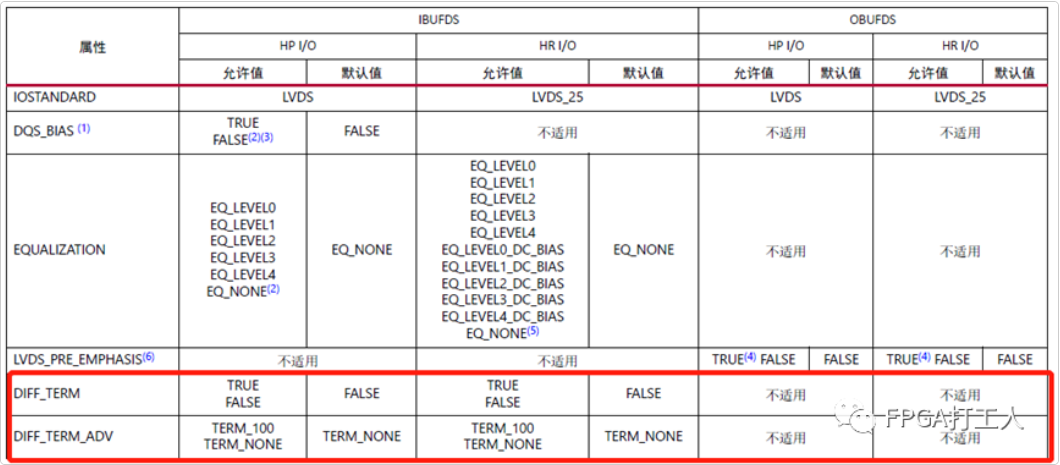

LVDS差分时钟

SATA 150M晶振没有焊接

| SATACLK_P | B10 |

|---|---|

| SATACLK_N | B9 |

| SFPCLK_P | C8 |

| SFPCLK_N | C7 |

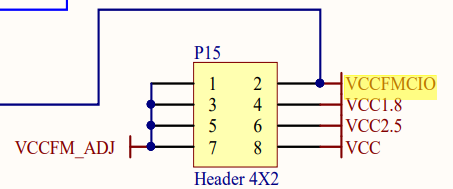

FMC

电平

根据跳线的连接不同电平也不一样,有1.8,2.5和3.3的

LPC部分

| 标注 | 原理图管脚名称 | FL4322对应信号 | 芯片IO号 | 标注 | 原理图管脚名称 | FL4322对应信号 | 芯片IO号 |

|---|---|---|---|---|---|---|---|

| C1 | GND | D1 | PG_C2M | ||||

| C2 | DP0_C2M_P | T29 | D2 | GND | |||

| C3 | DP0_C2M_N | T30 | D3 | GND | |||

| C4 | GND | D4 | GBTCLK0_M2C_P | R27 | |||

| C5 | GND | D5 | GBTCLK0_M2C_N | R28 | |||

| C6 | DP0_M2C_P | T33 | D6 | GND | |||

| C7 | DP0_M2C_N | T34 | D7 | GND | |||

| C8 | GND | D8 | LA01_CC_P | adc_data_p1[4] | G21 | ||

| C9 | GND | D9 | LA01_CC_N | adc_data_n1[4] | F21 | ||

| C10 | LA06_P | adc_data_p1[2] | J19 | D10 | GND | ||

| C11 | LA06_N | adc_data_n1[2] | J20 | D11 | LA05_P | adc_data_p1[7] | H18 |

| C12 | GND | D12 | LA05_N | adc_data_n1[7] | H19 | ||

| C13 | GND | D13 | GND | ||||

| C14 | LA10_P | adc_data_p1[10] | A21 | D14 | LA09_P | adc_data_p1[13] | D21 |

| C15 | LA10_N | adc_data_n1[10] | A22 | D15 | LA09_N | adc_data_n1[13] | C22 |

| C16 | GND | D16 | GND | ||||

| C17 | GND | D17 | LA13_P | dac_data_p[15] | F17 | ||

| C18 | LA14_P | dac_frame_p | B20 | D18 | LA13_N | dac_data_n[15] | F18 |

| C19 | LA14_N | dac_frame_n | A20 | D19 | GND | ||

| C20 | GND | D20 | LA17_CC_P | dac_dci_p | E17 | ||

| C21 | GND | D21 | LA17_CC_N | dac_dci_n | E18 | ||

| C22 | LA18_CC_P | fpga_clk_p | E19 | D22 | GND | ||

| C23 | LA18_CC_N | fpga_clk_n | D19 | D23 | LA23_P | dac_data_p[12] | D17 |

| C24 | GND | D24 | LA23_N | dac_data_n[12] | C17 | ||

| C25 | GND | D25 | GND | ||||

| C26 | LA27_P | dac_data_p[8] | B15 | D26 | LA26_P | dac_data_p[10] | B16 |

| C27 | LA27_N | dac_data_n[8] | A15 | D27 | LA26_N | dac_data_n[10] | A16 |

| C28 | GND | D28 | GND | ||||

| C29 | GND | D29 | FMC_TCK | ||||

| C30 | SCL | TRIG_to_fpga | AA8 | D30 | FMC_TDI | ||

| C31 | SDA | clk_spi_ce | W9 | D31 | FMC_TDO | ||

| C32 | GND | D32 | 3P3VAUX | ||||

| C33 | GND | D33 | FMC_TMS | ||||

| C34 | GND | D34 | FMC_TRST_L | ||||

| C35 | 12P0V | D35 | GA1 | AA3 | |||

| C36 | GND | D36 | 3P3V | ||||

| C37 | 12P0V | D37 | GND | ||||

| C38 | GND | D38 | 3P3V | ||||

| C39 | 3P3V | D39 | GND | ||||

| C40 | GND | D40 | 3P3V |

| 标注 | 原理图管脚名称 | FL4322对应信号 | 芯片IO号 | 标注 | 原理图管脚名称 | FL4322对应信号 | 芯片IO号 |

|---|---|---|---|---|---|---|---|

| G1 | GND | H1 | VREF_A_M2C | ||||

| G2 | CLK1_M2C_P | adc_data_p1[1] | AG5 | H2 | PRSNT_M2C_L | ||

| G3 | CLK1_M2C_N | adc_data_n1[1] | AG4 | H3 | GND | ||

| G4 | GND | H4 | CLK0_M2C_P | adc_data_p1[0] | AE5 | ||

| G5 | GND | H5 | CLK0_M2C_N | adc_data_n1[0] | AF5 | ||

| G6 | LA00_CC_P | adc_clk_p | G20 | H6 | GND | ||

| G7 | LA00_CC_N | adc_clk_n | F20 | H7 | LA02_P | adc_data_p1[3] | L17 |

| G8 | GND | H8 | LA02_N | adc_data_n1[3] | K17 | ||

| G9 | LA03_P | adc_data_p1[5] | L19 | H9 | GND | ||

| G10 | LA03_N | adc_data_n1[5] | K19 | H10 | LA04_P | adc_data_p1[6] | L18 |

| G11 | GND | H11 | LA04_N | adc_data_n1[6] | K18 | ||

| G12 | LA08_P | adc_data_p1[8] | J17 | H12 | GND | ||

| G13 | LA08_N | adc_data_n1[8] | H17 | H13 | LA07_P | adc_data_p1[9] | L20 |

| G14 | GND | H14 | LA07_N | adc_data_n1[9] | K20 | ||

| G15 | LA12_P | adc_data_p1[11] | J21 | H15 | GND | ||

| G16 | LA12_N | adc_data_n1[11] | H21 | H16 | LA11_P | adc_data_p1[12] | G18 |

| G17 | GND | H17 | LA11_N | adc_data_n1[12] | G19 | ||

| G18 | LA16_P | dac_data_p[13] | F16 | H18 | GND | ||

| G19 | LA16_N | dac_data_n[13] | F15 | H19 | LA15_P | adc_spi_ce | C21 |

| G20 | GND | H20 | LA15_N | dac_spi_ce | B21 | ||

| G21 | LA20_P | spi_io | C18 | H21 | GND | ||

| G22 | LA20_N | spi_clk | C19 | H22 | LA19_P | dac_data_p[14] | B18 |

| G23 | GND | H23 | LA19_N | dac_data_n[14] | B19 | ||

| G24 | LA22_P | dac_data_p[11] | E15 | H24 | GND | ||

| G25 | LA22_N | dac_data_n[11] | D15 | H25 | LA21_P | dac_data_p[7] | A17 |

| G26 | GND | H26 | LA21_N | dac_data_n[7] | A18 | ||

| G27 | LA25_P | dac_data_p[9] | D16 | H27 | GND | ||

| G28 | LA25_N | dac_data_n[9] | C16 | H28 | LA24_P | dac_data_p[6] | E14 |

| G29 | GND | H29 | LA24_N | dac_data_n[6] | D14 | ||

| G30 | LA29_P | dac_data_p[2] | C14 | H30 | GND | ||

| G31 | LA29_N | dac_data_n[2] | B14 | H31 | LA28_P | dac_data_p[5] | A13 |

| G32 | GND | H32 | LA28_N | dac_data_n[5] | A12 | ||

| G33 | LA31_P | dac_data_p[1] | C13 | H33 | GND | ||

| G34 | LA31_N | dac_data_n[1] | B13 | H34 | LA30_P | dac_data_p[4] | C12 |

| G35 | GND | H35 | LA30_N | dac_data_n[4] | B12 | ||

| G36 | LA33_P | dac_data_p[0] | F13 | H36 | GND | ||

| G37 | LA33_N | dac_data_n[0] | E13 | H37 | LA32_P | dac_data_p[3] | E12 |

| G38 | GND | H38 | LA32_N | dac_data_n[3] | D12 | ||

| G39 | VADJ | H39 | GND | ||||

| G40 | GND | H40 | VADJ | ||||

硬件约束

PL端DDR4

NODENAME PLDDR4_TEN , R142 1 U1 AD7 U26 N9 U27 N9

NODENAME PLDDR4_RESET_B , R137 1 U1 AF2 U26 P1 U27 P1

NODENAME PLDDR4_PAR , R115 1 U1 AE4 U26 T3 U27 T3

NODENAME PLDDR4_ODT , R133 1 U1 AG8 U26 K3 U27 K3

NODENAME PLDDR4_DQS3_T , U1 AL3 U27 B7

NODENAME PLDDR4_DQS3_C , U1 AL2 U27 A7

NODENAME PLDDR4_DQS2_T , U1 AN6 U27 G3

NODENAME PLDDR4_DQS2_C , U1 AP6 U27 F3

NODENAME PLDDR4_DQS1_T , U1 AN7 U26 B7

NODENAME PLDDR4_DQS1_C , U1 AP7 U26 A7

NODENAME PLDDR4_DQS0_T , U1 AP11 U26 G3

NODENAME PLDDR4_DQS0_C , U1 AP10 U26 F3

NODENAME PLDDR4_DQ31 , U1 AN1 U27 D7

NODENAME PLDDR4_DQ30 , U1 AL1 U27 D3

NODENAME PLDDR4_DQ29 , U1 AP3 U27 C8

NODENAME PLDDR4_DQ28 , U1 AK2 U27 C2

NODENAME PLDDR4_DQ27 , U1 AN3 U27 C7

NODENAME PLDDR4_DQ26 , U1 AK1 U27 C3

NODENAME PLDDR4_DQ25 , U1 AM1 U27 B8

NODENAME PLDDR4_DQ24 , U1 AK3 U27 A3

NODENAME PLDDR4_DQ23 , U1 AM6 U27 J7

NODENAME PLDDR4_DQ22 , U1 AM5 U27 J3

NODENAME PLDDR4_DQ21 , U1 AN4 U27 H8

NODENAME PLDDR4_DQ20 , U1 AK4 U27 H2

NODENAME PLDDR4_DQ19 , U1 AP4 U27 H7

NODENAME PLDDR4_DQ18 , U1 AM4 U27 H3

NODENAME PLDDR4_DQ17 , U1 AP5 U27 F7

NODENAME PLDDR4_DQ16 , U1 AK5 U27 G2

NODENAME PLDDR4_DQ15 , U1 AL8 U26 D7

NODENAME PLDDR4_DQ14 , U1 AK8 U26 D3

NODENAME PLDDR4_DQ13 , U1 AM8 U26 C8

NODENAME PLDDR4_DQ12 , U1 AJ9 U26 C2

NODENAME PLDDR4_DQ11 , U1 AL7 U26 C7

NODENAME PLDDR4_DQ10 , U1 AK7 U26 C3

NODENAME PLDDR4_DQ9 , U1 AM9 U26 B8

NODENAME PLDDR4_DQ8 , U1 AK9 U26 A3

NODENAME PLDDR4_DQ7 , U1 AM11 U26 J7

NODENAME PLDDR4_DQ6 , U1 AL10 U26 J3

NODENAME PLDDR4_DQ5 , U1 AM10 U26 H8

NODENAME PLDDR4_DQ4 , U1 AJ10 U26 H2

NODENAME PLDDR4_DQ3 , U1 AP9 U26 H7

NODENAME PLDDR4_DQ2 , U1 AN9 U26 F7

NODENAME PLDDR4_DQ1 , U1 AL11 U26 H3

NODENAME PLDDR4_DQ0 , U1 AK10 U26 G2

NODENAME PLDDR4_DM3 , U1 AN2 U27 E2

NODENAME PLDDR4_DM2 , U1 AL6 U27 E7

NODENAME PLDDR4_DM1 , U1 AN8 U26 E2

NODENAME PLDDR4_DM0 , U1 AJ12 U26 E7

NODENAME PLDDR4_CS_B , R148 1 U1 AG11 U26 L7 U27 L7

NODENAME PLDDR4_CKE , R112 1 U1 AF8 U26 K2 U27 K2

NODENAME PLDDR4_CK_T , R108 1 U1 AH1 U26 K7 U27 K7

NODENAME PLDDR4_CK_C , R109 1 U1 AJ1 U26 K8 U27 K8

NODENAME PLDDR4_BG0 , R107 1 U1 AH7 U26 M2 U27 M2

NODENAME PLDDR4_BA1 , R105 1 U1 AG9 U26 N8 U27 N8

NODENAME PLDDR4_BA0 , R101 1 U1 AF12 U26 N2 U27 N2

NODENAME PLDDR4_ALERT_B , R121 1 U1 AF3 U26 P9 U27 P9

NODENAME PLDDR4_ACT_B , R120 1 U1 AH8 U26 L3 U27 L3

NODENAME PLDDR4_A16_RAS_B , R99 1 U1 AF1 U26 L8 U27 L8

NODENAME PLDDR4_A15_CAS_B , R98 1 U1 AF10 U26 M8 U27 M8

NODENAME PLDDR4_A14_WE_B , R97 1 U1 AD2 U26 L2 U27 L2

NODENAME PLDDR4_A13 , R96 1 U1 AG3 U26 T8 U27 T8

NODENAME PLDDR4_A12 , R95 1 U1 AH11 U26 M7 U27 M7

NODENAME PLDDR4_A11 , R94 1 U1 AD10 U26 T2 U27 T2

NODENAME PLDDR4_A10 , R93 1 U1 AD6 U26 M3 U27 M3

NODENAME PLDDR4_A9 , R88 1 U1 AH2 U26 R7 U27 R7

NODENAME PLDDR4_A8 , R86 1 U1 AE8 U26 R2 U27 R2

NODENAME PLDDR4_A7 , R85 1 U1 AH3 U26 R8 U27 R8

NODENAME PLDDR4_A6 , R83 1 U1 AF11 U26 P2 U27 P2

NODENAME PLDDR4_A5 , R64 1 U1 AH6 U26 P8 U27 P8

NODENAME PLDDR4_A4 , R62 1 U1 AG6 U26 N3 U27 N3

NODENAME PLDDR4_A3 , R61 1 U1 AG10 U26 N7 U27 N7

NODENAME PLDDR4_A2 , R60 1 U1 AJ2 U26 R3 U27 R3

NODENAME PLDDR4_A1 , R59 1 U1 AD5 U26 P7 U27 P7

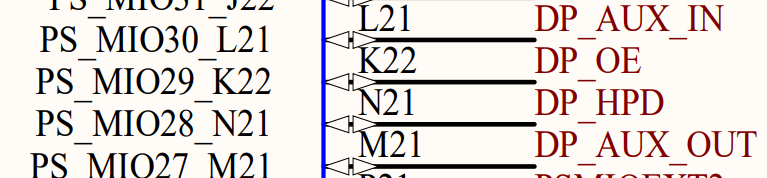

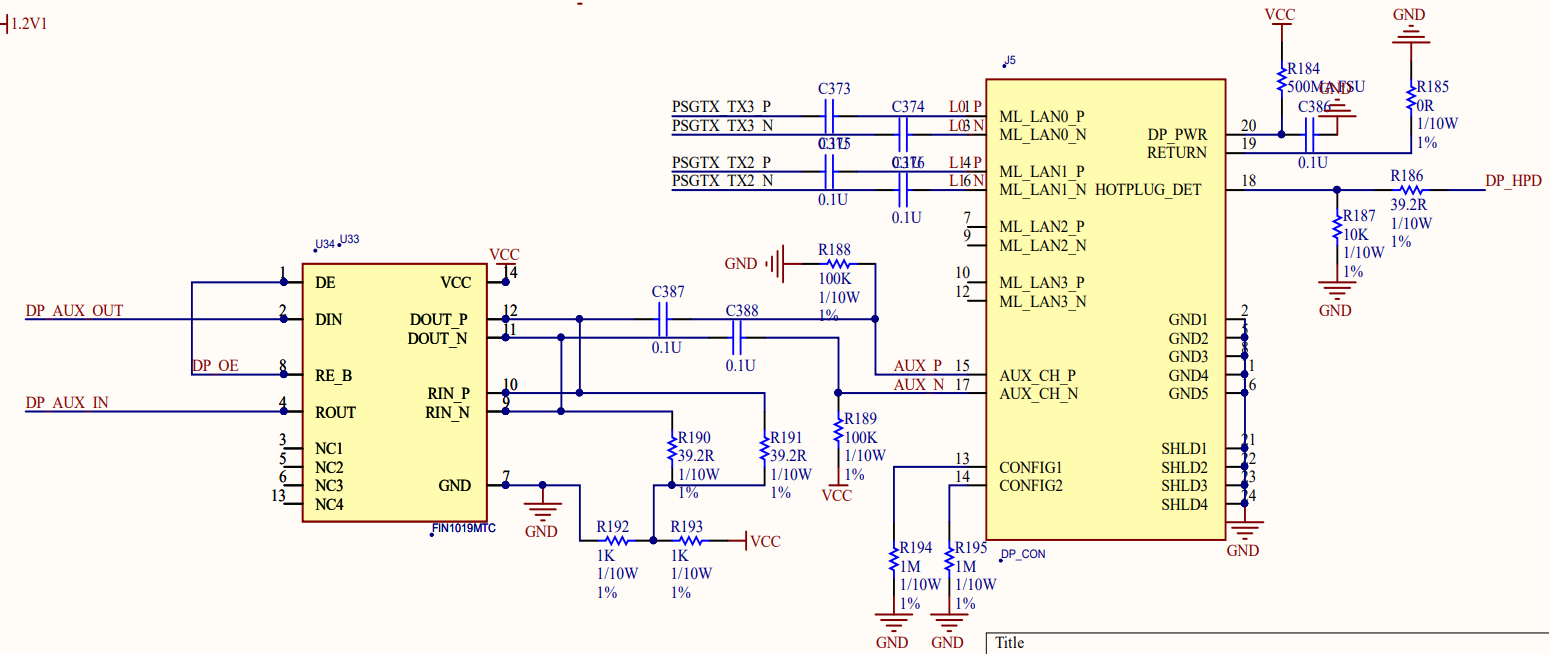

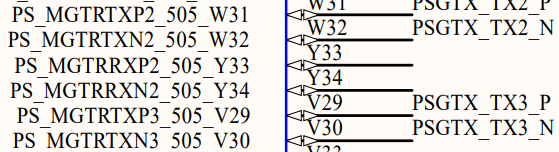

NODENAME PLDDR4_A0 , R58 1 U1 AD4 U26 P3 U27 P3DP显示接口

Comments NOTHING